Thiết bị định tuyến tăng tốc bảo mật

Sáng chế về “Thiết bị định tuyến tăng tốc bảo mật dùng phần cứng mảng phần tử logic người dùng có thể lập trình được (FPGA)”.

Tác giả: Hoàng Trang, Bùi Quốc Bảo, Trần Hoàng Linh.

Số bằng: 1-0037864.

Ngày công bố: 25/12/2023.

Chủ bằng: Trường Đại học Bách Khoa (ĐHQG-HCM).

Sáng chế đề cập đến thiết bị định tuyến tăng tốc bảo mật dùng phần cứng dùng mảng phần tử logic người dùng có thể lập trình được (FPGA), thiết bị theo sáng chế có khả năng cung cấp kết nối bảo mật trên nền tảng mạng riêng ảo (VPN) với tốc độ cao. Thiết bị định tuyến tăng tốc bảo mật này cung cấp nhiều cổng giao tiếp LAN (Local Network Area - Mạng cục bộ), một cổng giao tiếp WAN (Wide Area Network - Mạng diện rộng) và một cổng giao tiếp quang, tất cả đều hỗ trợ tốc độ Gigabit. Bo mạch chính của thiết bị gồm vi xử lý Marvell 88F6820 đảm nhiệm các tác vụ chính; chip chuyển mạch 88E6176 cho phép mở rộng 05 cổng LAN. Các thiết bị ngoại vi khác gồm một cổng nối tiếp và EJTAG để gỡ rối chương trình; hai cổng USB để kết nối thiết bị ngoại vi. Bộ nhớ lưu trữ chính là eMMC có dung lượng 8 Gbit. Ngoài ra, bo mạch chính có giao tiếp SATA (Serial Advanced Technology Attachment) để kết nối ổ đĩa cứng; giao tiếp SDIO (Secure Digital Input Output) để kết nối với SD CARD (Secure Digital Card). Để tăng tốc cho thiết bị, toàn bộ quá trình tính toán bảo mật theo chuẩn IPsec được đưa vào một môđun FPGA, kết nối với bo mạch chính qua giao tiếp mini PCIe.

Đọc toàn văn:

https://ipvietnam.gov.vn/documents/20182/1616475/37864.pdf/896793bd-190b-43c0-aefe-bda370525405

Thiết bị định tuyến tăng tốc bảo mật

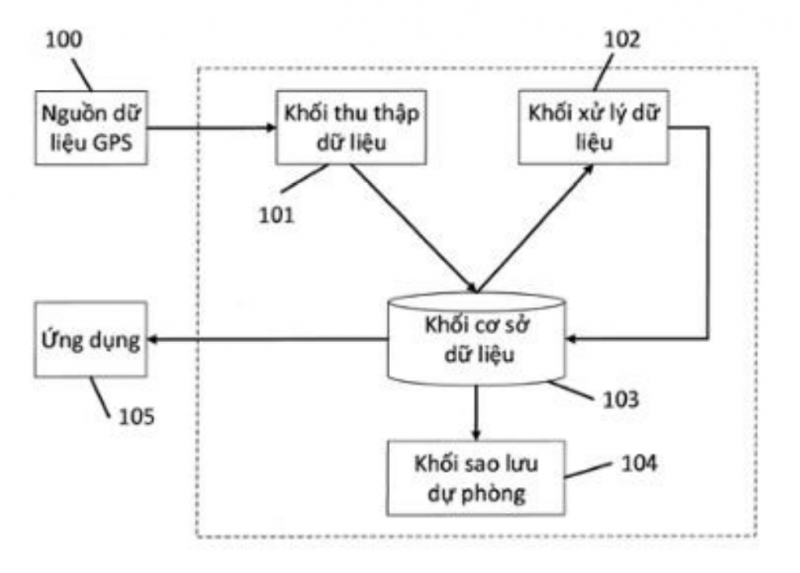

Dữ liệu định vị toàn cầu theo thời gian thực

Giải pháp hữu ích về “Hệ thống và phương pháp xử lý dữ liệu định vị toàn cầu (GPS) theo thời gian thực dùng cho hệ thống giao thông thông minh”.

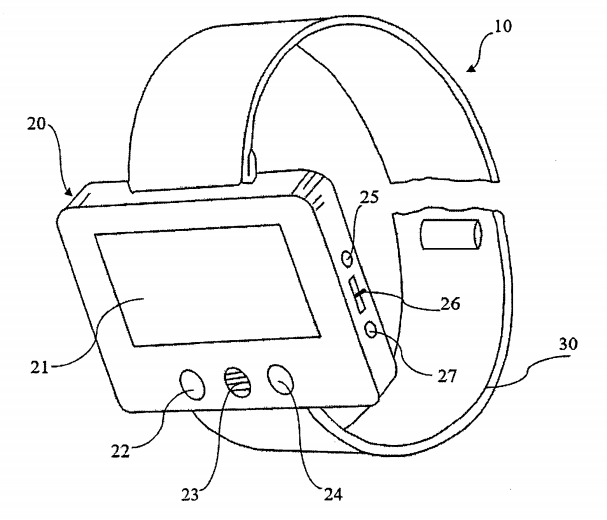

Thiết bị đeo tay cảnh báo

Giải pháp hữu ích về “Thiết bị đeo tay cảnh báo các tham số của lồng ấp trẻ sơ sinh bằng công nghệ truyền không dây ZigBee”.

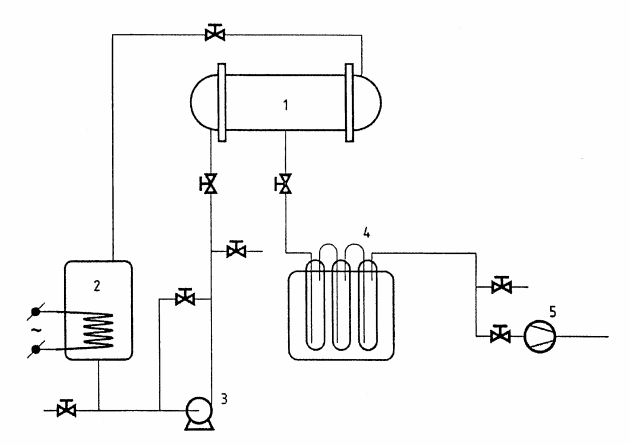

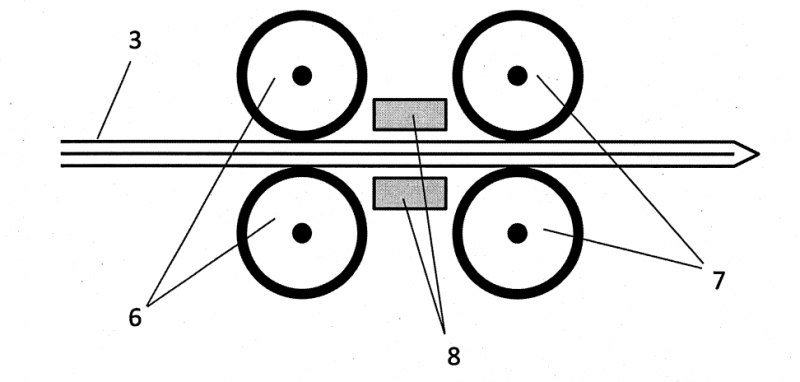

Hệ thống khử nước dung dịch cồn cao độ

Giải pháp hữu ích về “Hệ thống khử nước dung dịch cồn cao độ bằng công nghệ thẩm thấu bốc hơi sử dụng màng ống”.

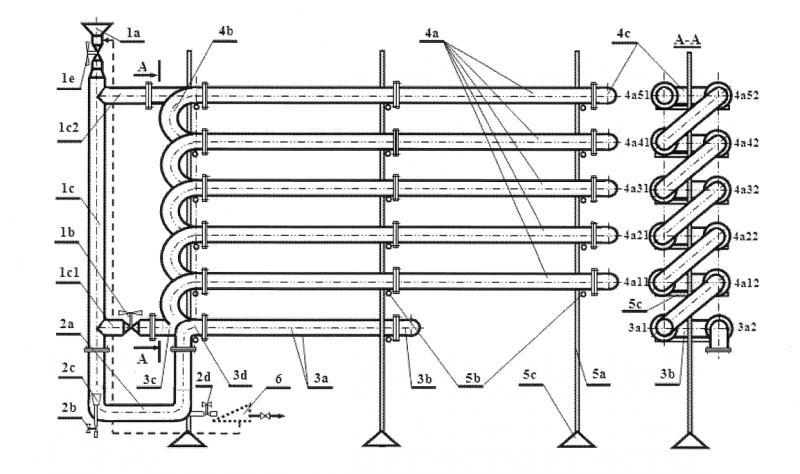

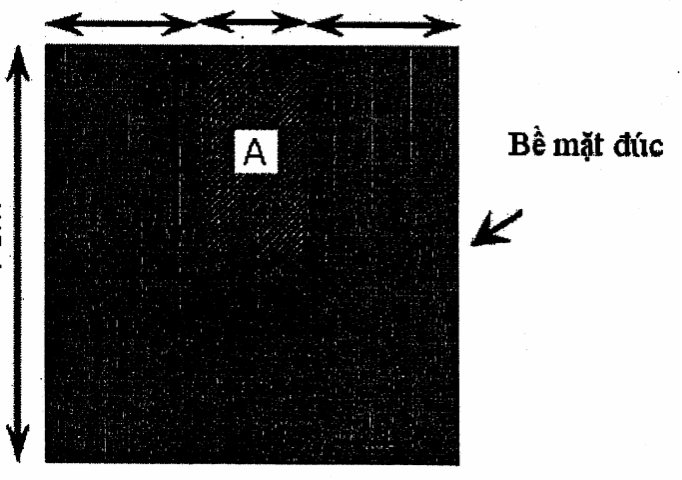

Thiết bị nuôi tảo đơn bào

Giải pháp hữu ích về “Thiết bị nuôi tảo đơn bào dạng ống nhiều tầng”.

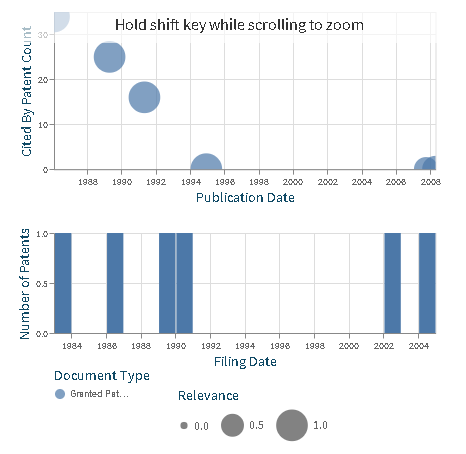

Sáng chế về virus corona từ cơ sở dữ liệu Lens

- Từ khoá sử dụng: corona, virus.

- Kết quả tra cứu được ghi theo chuẩn IEEE dạng Web Page, có đính kèm link truy cập toàn văn.

Theo dõi sức khoẻ công trình xây dựng

Sáng chế về “Cảm biến áp lực hữu cơ bằng vật liệu polyme để theo dõi sức khỏe công trình xây dựng và hệ thống tự động theo dõi sức khỏe công trình xây dựng sử dụng cảm biến này”.

Xi măng Composit chịu Sulfat hoặc nước biển

Sáng chế về “Xi măng Composit có độ bền chịu Sulfat và/hoặc chịu nước biển”.

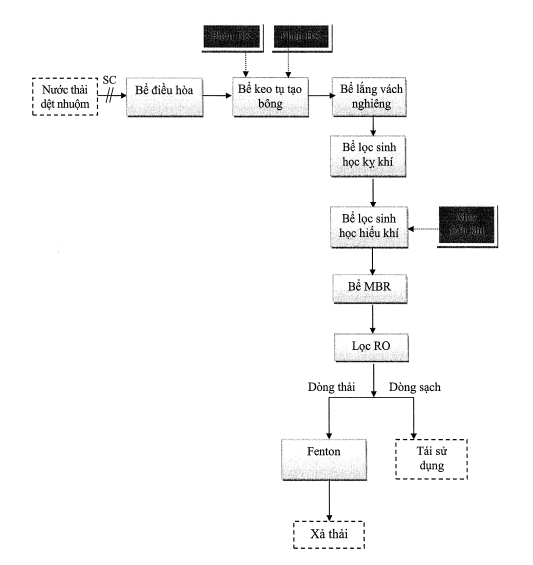

Hệ thống xử lý nước thải dệt nhuộm

Giải pháp hữu ích về “Hệ thống xử lý nước thải dệt nhuộm”.

Phương pháp xử lý nước thải y tế

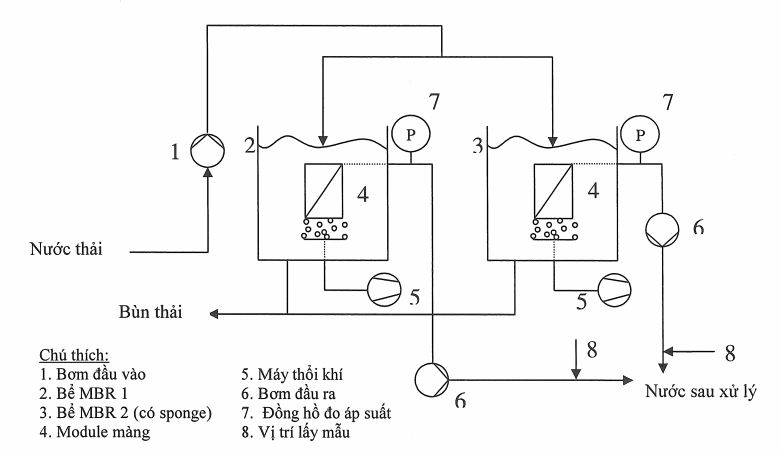

Giải pháp hữu ích về “Phương pháp xử lý nước thải y tế bằng màng sinh học (Membrane Bio Reactor, MBR) kết hợp giá thể di động (Sponge)”.

- Vòng Sơ Khảo Cuộc Thi Đại Sứ Văn Hóa Đọc Năm 2024

- Hoạt động chào mừng "Ngày sách Việt Nam 21/4/2024"

- Ngày hội văn hóa đọc lần V

- Cuộc Thi Ảnh “Khoảnh Khắc VNUHCM Libraries”

- Ngày hội văn hóa đọc lần II

- Ngày hội văn hóa đọc lần IV

- Ngày hội văn hóa đọc lần III

- Tiếp GS Omer Mert Denizci, Trường ĐH Marmara Thổ Nhĩ Kỳ

- Tiếp Cô Claudia Tarzariol Từ The University Of Trento, Italy (Unitrento)

- Tiến sĩ kiều bào Mỹ tặng sách trị giá 150.000 USD cho sinh viên bách khoa

- Khảo sát ý kiến bạn đọc

-

Trực tuyến:12

-

Hôm nay:5153

-

Tuần này:32131

-

Tuần trước:28342

-

Tháng trước:57565

-

Tất cả:4021234

.png)

.png)